# **CPC510**

# 3U Compact PCI CPU Board

# **User Manual**

**Revision 1.00**

The product described in this manual is compliant with all related CE standards.

#### CPC510 CPU Board

Product Title: CPC510 Document name: CPC510 User Manual Manual version: 1.00 Reference document: IMEC.421459.510

Copyright © 2012, 2013 Fastwel Co. Ltd. All rights reserved.

# **Revision Record**

| Revision No. | Brief description of changes | Board index | Revision date |

|--------------|------------------------------|-------------|---------------|

| 1.00         | Initial version              | CPC510      | April 2013    |

|              |                              |             |               |

|              |                              |             |               |

|              |                              |             |               |

### **Contact Information**

|          | Fastwel Co. Ltd         | Fastwel Corporation US   |

|----------|-------------------------|--------------------------|

| Address: | 108 Profsoyuznaya st.,  | 55 Washington St. #310   |

|          | Moscow 117437,          | Brooklyn, New York 11201 |

|          | Russian Federation      | USA                      |

| Tel.:    | +7 (495) 232-1681       | +1 (718) 554-3686        |

| Fax:     | +7 (495) 232-1654       | +1 (718) 797-0600        |

| E-mail:  | info@fastwel.com        | sales@fastwel.com        |

| Web:     | http://www.fastwel.com/ | http://www.fastwel.com/  |

# TABLE OF CONTENTS

| TRADEMARKS                                                         | 7                                |    |

|--------------------------------------------------------------------|----------------------------------|----|

| OWNERSHIP RIGHTS                                                   | -                                | 7  |

| COPYRIGHT.                                                         |                                  |    |

| NOTATIONS.<br>TRANSPORTATION, UNPACKING AND STORAGE                |                                  |    |

| Transportation.                                                    |                                  |    |

| Unpacking                                                          |                                  | 10 |

| Storage                                                            |                                  | 10 |

| MANUFACTURER'S WARRANTY                                            |                                  | 11 |

| Warranty Liability                                                 |                                  |    |

| Liability Limitation Right                                         |                                  |    |

| Warranty Period                                                    |                                  | 11 |

| Limitation of warranty liabilities                                 |                                  |    |

| Returning a product for repair                                     |                                  |    |

| 1. INTRODUCTION                                                    |                                  |    |

| 1.1. Overview                                                      |                                  |    |

| 1.2. Technical characteristics                                     |                                  | 13 |

| 1.3. CPC510 hardware configurations                                |                                  | 15 |

| 1.4. Delivery checklist                                            |                                  |    |

| 1.5. Package                                                       |                                  |    |

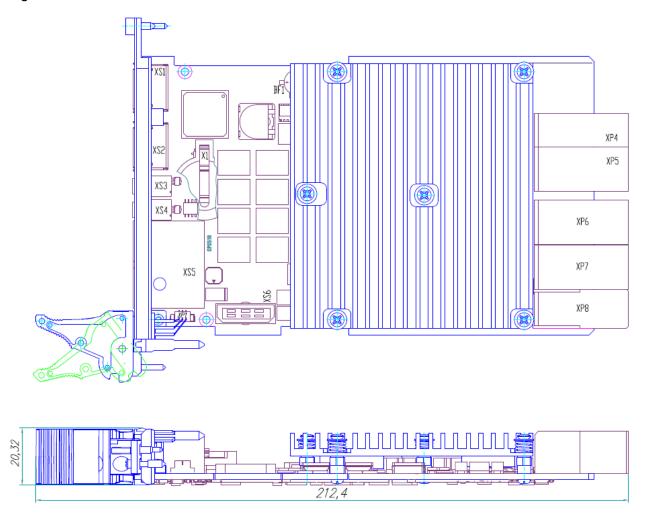

| 1.6. External view and element layout                              |                                  |    |

| 1.6.1 External view of CPC510                                      |                                  |    |

| 1.6.2 Layout of main components                                    |                                  |    |

| 1.6.3 Front panel<br>2. SPECIFICATIONS                             |                                  |    |

| 2.1. Block diagram                                                 |                                  |    |

| 2.2. Peculiarities of functional units                             |                                  |    |

| 2.3 System extension possibilities                                 |                                  |    |

| 2.4 Peripherals                                                    |                                  |    |

| 2.4.1 Timers                                                       |                                  |    |

| 2.4.1.1 Watchdog timer                                             |                                  |    |

| 2.4.2 Battery                                                      |                                  |    |

| 2.4.3 Devices on local SMBus                                       |                                  |    |

| 2.4.4 Nonvolatile memory                                           |                                  |    |

| 2.4.4.1 MicroSD                                                    |                                  |    |

| 2.4.4.2 High-speed FRAM memory for storing user dat                | е                                | 37 |

| 2.2.4.2.2. FRAM module programming                                 |                                  | 38 |

| 2.5 Board interfaces                                               |                                  |    |

| 2.5.1 CompactPCI Serial connectors                                 |                                  | 40 |

| 2.5.2 Connector for mezzanine board installation                   |                                  |    |

| 2.5.3 Keyboard/mouse interface                                     |                                  |    |

| 2.5.4 USB interfaces                                               |                                  |    |

| 2.5.5 DisplayPort                                                  |                                  |    |

| 2.5.6 Serial interfaces (RS-232 u RS-485)                          |                                  |    |

| 2.5.7 Parallel port interface                                      |                                  |    |

| 2.5.8 Gigabit Ethernet interface                                   |                                  |    |

| 2.5.8.1 Purpose of RJ45 connector contacts                         |                                  |    |

| 2.5.8.2 Status LEDs of Ethernet channel<br>2.5.9 MicroSD connector |                                  |    |

| 2.5.10 SATA interface                                              |                                  |    |

| 2.5.11 HD (high definition) audio                                  |                                  |    |

| 2.6. LEDs                                                          |                                  |    |

| 2.6.1 GP LED configuration and control registers (logical          |                                  |    |

| 2.6.2 LED register initialization                                  |                                  |    |

| 2.6.2.1 Designation of separate bits of the LED registe            |                                  |    |

| 3. APPLICATION OF CPC 510                                          |                                  |    |

| 3.1 Compact PCI Serial system                                      |                                  |    |

| 3.1.1 Board-to-board connections                                   |                                  |    |

| 3.1.2 Interaction with power supply unit                           |                                  |    |

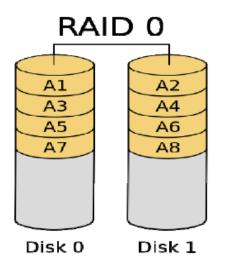

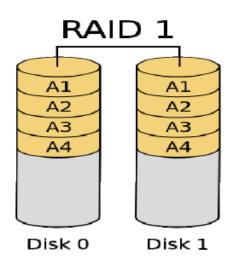

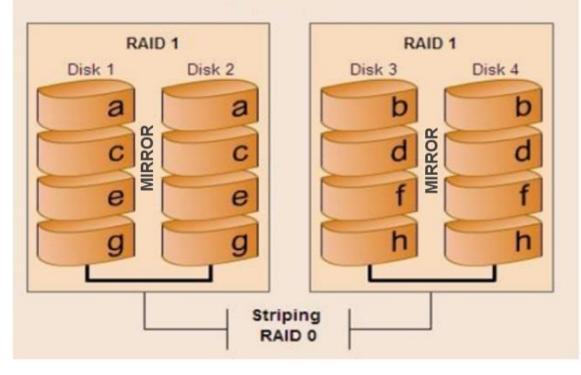

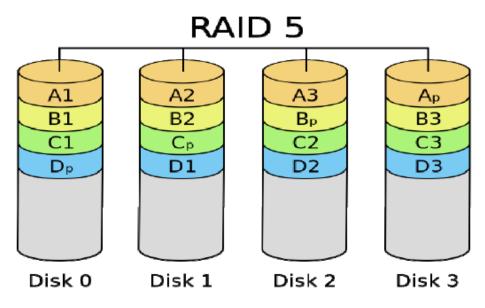

| 3.1.3 Peculiarities of information storage system                  |                                  |    |

| CPC510 3U Compact PCI CPU Board                                    | © 2 0 1 4 F a s t w e I Ver.1.00 |    |

| 3.2.1 Power supply unit.       63         3.2.2 Peculiarities of data storage system implementation.       63         3.2.3 Using CPC510-01 as additional computing device.       64         3.3. Extended hybrid Compact PCI Serial system.       65         3.4 Additional features of CPC510.       66         4.1 Safety requirements.       67         4.1 Safety requirements.       67         4.2 Installation procedure       69         4.4 Installation of CPC510 peripheral devices.       70         4.4.1 Installation of MicroSD memory cards.       70         4.4.2 Connection of USB devices.       70         4.4.3 Battery replacement.       71         4.5 Installation of MiCroSD memory cards.       70         4.4.3 Battery replacement.       71         4.5 Installation of MiCroSD memory cards.       70         4.4.3 Battery replacement.       71         4.5 Installation of MiCroSD.       72         5 Installation of Software.       72         5.1 Operating mode of PCI-Express.       72         5.2 Reset of BIOS to factory settings and switching over to Transparent mode.       72         7.1 Temperature mode control.       75         7.1.1 Passive temperature control.       75         7.1.2 Heat dissipation by heat sink and system en | 3.2 Compact PCI Plus I/O system6                          | 1   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----|

| 3.2.3 Using CPC510-01 as additional computing device.       64         3.3. Extended hybrid Compact PCI Serial system       65         3.4 Additional features of CPC510.       66         4.INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                           |     |

| 3.3. Extended hybrid Compact PCI Serial system       .65         3.4 Additional features of CPC510       .66         4. INSTALLATION       .67         4.1 Safety requirements       .67         4.2 Installation procedure of CPC510       .68         4.3 Board removal procedure.       .69         4.4.1 Installation of CPC510 peripheral devices       .70         4.4.1 Installation of MicroSD memory cards       .70         4.4.2 Connection of USB devices       .70         4.4.3 Battery replacement       .71         4.5 Installation of MIC584 mezzanine board       .71         4.6 Installation of Software       .71         5.1 Operating mode of PCI-Express       .72         5.2 Reset of BIOS to factory settings and switching over to Transparent mode       .72         5.1 Apperature mode control       .75         7.1 Temperature mode control       .75         7.1.1 Passive temperature control       .75         7.1.2 Heat dissipation by heat sink and system enclosure       .76         7.1 Dever consumption of CPC510.       .77         7.3 Compliance with safety requirements for CPC510.       .77         7.4 Operating conditions.       .76         7.4 Operating conditions.       .76         7.4 Operating conditions.       .77           | 3.2.2 Peculiarities of data storage system implementation | 63  |

| 3.4 Additional features of CPC510                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                           |     |

| 4. INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |     |

| 4.1 Safety requirements.       67         4.2 Installation procedure of CPC510.       68         4.3 Board removal procedure.       69         4.4 Installation of CPC510 peripheral devices.       70         4.4.1 Installation of MicroSD memory cards.       70         4.4.1 Installation of USB devices.       70         4.4.2 Connection of USB devices.       70         4.4.3 Battery replacement.       71         4.5 Installation of MIC584 mezzanine board.       71         4.6 Installation of Software.       71         5 SYSTEM SETTINGS.       72         5.1 Operating mode of PCI-Express.       72         5.2 Reset of BIOS to factory settings and switching over to Transparent mode.       72         6. PHOENIX® BIOS.       74         7. ADDITIONAL INFORMATION       75         7.1.1 Passive temperature control.       75         7.1.2 Heat dissipation by heat sink and system enclosure.       76         7.1.3 Board cooling recommendations.       77         7.4 Operating conditions.       77         7.5 Cooling system requirements for CPC510.       77         7.4 Operating conditions.       77         7.5 Cooling system requirements.       78         ANIC590 Board.       79         A1 Introduction.<                                    |                                                           |     |

| 4.2 Installation procedure of CPC510.       68         4.3 Board removal procedure       69         4.4 Installation of CPC510 peripheral devices.       70         4.4.1 Installation of MicroSD memory cards.       70         4.4.2 Connection of USB devices.       70         4.4.3 Battery replacement.       71         4.5 Installation of MIC584 mezzanine board.       71         4.6 Installation of software.       71         5 SYSTEM SETTINGS.       72         5.1 Operating mode of PCI-Express.       72         5.1 Operating mode of PCI-Express.       72         5.2 Reset of BIOS to factory settings and switching over to Transparent mode.       72         6. PHOENIX® BIOS.       74         7.1 ADDITIONAL INFORMATION       75         7.1.1 Passive temperature control.       75         7.1.2 Heat dissipation by heat sink and system enclosure.       76         7.1.3 Board cooling recommendations.       76         7.2 Power consumption of CPC510.       77         7.4 Operating conditions.       77         7.5 Cooling system requirements for CPC510.       77         7.4 Operating conditions.       77         7.5 Cooling system requirements.       78         ANIC590 Board.       79         A.1 Intro                                    |                                                           |     |

| 4.3 Board removal procedure       69         4.4 Installation of CPC510 peripheral devices       70         4.4.1 Installation of MicroSD memory cards       70         4.4.2 Connection of USB devices       70         4.4.3 Battery replacement       71         4.5 Installation of MIC584 mezzanine board       71         4.6 Installation of software       71         5 SYSTEM SETTINGS       72         5.1 Operating mode of PCI-Express       72         5.2 Reset of BIOS to factory settings and switching over to Transparent mode       72         6.PHOENIX® BIOS       74         7. ADDITIONAL INFORMATION       75         7.1.1 Passive temperature control.       75         7.1.2 Heat dissipation by heat sink and system enclosure.       76         7.1.3 Board cooling recommendations.       76         7.2 Power consumption of CPC510.       77         7.4 Operating conditions.       77         7.5 Cooling system requirements for CPC510.       77         7.4 Operating conditions.       77         7.5 Cooling system requirements.       78         ANNEX A.       79         A MIC590 Board.       79         A.1 Introduction.       79         A.2 MIC590 functional capabilities.       79 <td></td> <td></td>                                      |                                                           |     |

| 4.4 Installation of CPC510 peripheral devices       70         4.4.1 Installation of MicroSD memory cards       70         4.4.2 Connection of USB devices       70         4.4.3 Battery replacement       71         4.5 Installation of MIC584 mezzanine board       71         4.6 Installation of software       71         5 SYSTEM SETTINGS       72         5.1 Operating mode of PCI-Express       72         5.2 Reset of BIOS to factory settings and switching over to Transparent mode       72         5.2 Reset of BIOS       74         7. ADDITIONAL INFORMATION       75         7.1.1 Passive temperature control       75         7.1.2 Heat dissipation by heat sink and system enclosure       76         7.1.3 Board cooling recommendations       76         7.4 Operating conditions       77         7.5 Cooling system requirements for CPC510       77         7.4 Operating conditions       78         ANNEX A       79         A.1 Introduction       79         A.2 MIC590 Board       79         A.3 External view of MIC590 mezzanine board       80         A.4 Functional units of MIC590 board       80         A.4 Functional units of MIC590 board       80                                                                                            |                                                           |     |

| 4.4.1 Installation of MicroSD memory cards       70         4.4.2 Connection of USB devices       70         4.4.3 Battery replacement       71         4.5 Installation of MIC584 mezzanine board       71         4.6 Installation of software       71         5 SYSTEM SETTINGS       72         5.1 Operating mode of PCI-Express.       72         5.2 Reset of BIOS to factory settings and switching over to Transparent mode.       72         6 PHOENIX® BIOS       74         7 ADDITIONAL INFORMATION       75         7.1.1 Passive temperature control.       75         7.1.2 Heat dissipation by heat sink and system enclosure       76         7.1.3 Board cooling recommendations.       76         7.4 Operating system requirements for CPC510.       77         7.5 Cooling system requirements.       78         ANNEX A.       79         A.1 Introduction.       79         A.2 MIC590 functional capabilities.       79         A.3 External view of MIC590 mezzanine board       80         A.4 Functional units of MIC590 board       81         A.5 CompactPCI connector of MIC590 board       81                                                                                                                                                                | 4.3 Board removal procedure                               | .69 |

| 4.4.2 Connection of USB devices       70         4.4.3 Battery replacement       71         4.5 Installation of MIC584 mezzanine board       71         4.6 Installation of software       71         5.1 Operating mode of PCI-Express       72         5.1 Operating mode of PCI-Express       72         5.2 Reset of BIOS to factory settings and switching over to Transparent mode       72         6. PHOENIX® BIOS       74         7. ADDITIONAL INFORMATION       75         7.1.1 Passive temperature control       75         7.1.2 Heat dissipation by heat sink and system enclosure       76         7.1.3 Board cooling recommendations       76         7.2 Power consumption of CPC510       77         7.4 Operating conditions       77         7.5 Cooling system requirements for CPC510       77         7.5 Cooling system requirements       79         A MIC590 Board       79         A MIC590 Board       79         A.1 Introduction       79         A.2 MIC590 functional capabilities       79         A.3 External view of MIC590 mezzanine board       80         A.4 Functional units of MIC590 board       81                                                                                                                                             |                                                           |     |

| 4.4.3 Battery replacement.       71         4.5 Installation of MIC584 mezzanine board.       71         4.6 Installation of software.       71         5 SYSTEM SETTINGS.       72         5.1 Operating mode of PCI-Express.       72         5.2 Reset of BIOS to factory settings and switching over to Transparent mode.       72         6. PHOENIX® BIOS       74         7. ADDITIONAL INFORMATION       75         7.1.1 Passive temperature control.       75         7.1.2 Heat dissipation by heat sink and system enclosure.       76         7.1.3 Board cooling recommendations.       76         7.2 Power consumption of CPC510.       77         7.3 Compliance with safety requirements for CPC510.       77         7.4 Operating conditions.       76         7.5 Cooling system requirements.       78         ANNEX A.       79         A MIC590 Board.       79         A.1 Introduction.       79         A.2 MIC590 functional capabilities.       79         A.3 External view of MIC590 mezzanine board.       80         A.4 Functional units of MIC590 board.       81                                                                                                                                                                                          | 4.4.1 Installation of MicroSD memory cards                | 70  |

| 4.5 Installation of MIC584 mezzanine board.       71         4.6 Installation of software.       71         5 SYSTEM SETTINGS.       72         5.1 Operating mode of PCI-Express.       72         5.2 Reset of BIOS to factory settings and switching over to Transparent mode.       72         6. PHOENIX® BIOS.       74         7. ADDITIONAL INFORMATION       75         7.1.1 Passive temperature control.       75         7.1.2 Heat dissipation by heat sink and system enclosure.       76         7.1.3 Board cooling recommendations.       76         7.2 Power consumption of CPC510.       77         7.3 Compliance with safety requirements for CPC510.       77         7.5 Cooling system requirements.       78         ANNEX A.       79         A MIC590 Board.       79         A.1 Introduction.       79         A.2 MIC590 functional capabilities.       79         A.3 External view of MIC590 mezzanine board.       80         A.4 Functional units of MIC590 board.       81         A.5 CompactPCI connector of MIC590 board.       83                                                                                                                                                                                                                     |                                                           |     |

| 4.6 Installation of software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.4.3 Battery replacement                                 | .71 |

| 5 SYSTEM SETTINGS.725.1 Operating mode of PCI-Express.725.2 Reset of BIOS to factory settings and switching over to Transparent mode.726. PHOENIX® BIOS.747. ADDITIONAL INFORMATION.757.1 Temperature mode control.757.1.1 Passive temperature control.757.1.2 Heat dissipation by heat sink and system enclosure.767.1.3 Board cooling recommendations.767.2 Power consumption of CPC510.777.3 Compliance with safety requirements for CPC510.777.4 Operating conditions.777.5 Cooling system requirements.78ANNEX A.79A MIC590 Board.79A.1 Introduction.79A.2 MIC590 functional capabilities.79A.3 External view of MIC590 mezzanine board.80A.4 Functional units of MIC590.81A.5 CompactPCI connector of MIC590 board.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                           |     |

| 5.1 Operating mode of PCI-Express       .72         5.2 Reset of BIOS to factory settings and switching over to Transparent mode       .72         6. PHOENIX® BIOS       .74         7. ADDITIONAL INFORMATION       .75         7.1 Temperature mode control.       .75         7.1.1 Passive temperature control.       .75         7.1.2 Heat dissipation by heat sink and system enclosure       .76         7.1.3 Board cooling recommendations.       .76         7.2 Power consumption of CPC510.       .77         7.3 Compliance with safety requirements for CPC510.       .77         7.4 Operating conditions       .77         7.5 Cooling system requirements.       .78         ANNEX A.       .79         A MIC590 Board.       .79         A.1 Introduction.       .79         A.2 MIC590 functional capabilities.       .79         A.3 External view of MIC590 mezzanine board.       .80         A.4 Functional units of MIC590 board.       .81         A.5 CompactPCI connector of MIC590 board.       .83                                                                                                                                                                                                                                                             |                                                           |     |

| 5.2 Reset of BIOS to factory settings and switching over to Transparent mode.       72         6. PHOENIX® BIOS.       74         7. ADDITIONAL INFORMATION       75         7.1 Temperature mode control.       75         7.1.1 Passive temperature control.       75         7.1.2 Heat dissipation by heat sink and system enclosure.       76         7.1.3 Board cooling recommendations.       76         7.2 Power consumption of CPC510.       77         7.3 Compliance with safety requirements for CPC510.       77         7.5 Cooling system requirements.       78         ANNEX A.       79         A MIC590 Board.       79         A.1 Introduction.       79         A.2 MIC590 functional capabilities.       79         A.3 External view of MIC590 mezzanine board.       80         A.4 Functional units of MIC590 board.       81                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                           |     |

| 6. PHOENIX® BIOS       74         7. ADDITIONAL INFORMATION       75         7.1 Temperature mode control.       75         7.1.1 Passive temperature control.       75         7.1.2 Heat dissipation by heat sink and system enclosure.       76         7.1.3 Board cooling recommendations.       76         7.2 Power consumption of CPC510       77         7.3 Compliance with safety requirements for CPC510.       77         7.4 Operating conditions.       77         7.5 Cooling system requirements.       78         ANNEX A.       79         A IIntroduction.       79         A.1 Introduction.       79         A.2 MIC590 functional capabilities.       79         A.3 External view of MIC590 mezzanine board.       80         A.4 Functional units of MIC590.       81         A.5 CompactPCI connector of MIC590 board.       83                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                           |     |

| 7. ADDITIONAL INFORMATION       75         7.1 Temperature mode control       75         7.1.1 Passive temperature control.       75         7.1.2 Heat dissipation by heat sink and system enclosure       76         7.1.3 Board cooling recommendations.       76         7.2 Power consumption of CPC510.       77         7.3 Compliance with safety requirements for CPC510.       77         7.4 Operating conditions.       77         7.5 Cooling system requirements.       78         ANNEX A.       79         A.1 Introduction.       79         A.2 MIC590 Board.       79         A.3 External view of MIC590 mezzanine board.       80         A.4 Functional units of MIC590.       81         A.5 CompactPCI connector of MIC590 board.       83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                           |     |

| 7.1 Temperature mode control.757.1.1 Passive temperature control.757.1.2 Heat dissipation by heat sink and system enclosure.767.1.3 Board cooling recommendations.767.2 Power consumption of CPC510.777.3 Compliance with safety requirements for CPC510.777.4 Operating conditions.777.5 Cooling system requirements.78ANNEX A.79A MIC590 Board.79A.1 Introduction.79A.2 MIC590 functional capabilities.79A.3 External view of MIC590 mezzanine board.80A.4 Functional units of MIC590.81A.5 CompactPCI connector of MIC590 board.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                           |     |

| 7.1.1 Passive temperature control.757.1.2 Heat dissipation by heat sink and system enclosure.767.1.3 Board cooling recommendations.767.1.3 Board cooling recommendations.777.3 Compliance with safety requirements for CPC510.777.4 Operating conditions.777.5 Cooling system requirements.78ANNEX A.79A MIC590 Board.79A.1 Introduction.79A.2 MIC590 functional capabilities.79A.3 External view of MIC590 mezzanine board.80A.4 Functional units of MIC590.81A.5 CompactPCI connector of MIC590 board.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |     |

| 7.1.2 Heat dissipation by heat sink and system enclosure767.1.3 Board cooling recommendations767.1.3 Board cooling recommendations767.2 Power consumption of CPC510777.3 Compliance with safety requirements for CPC510777.4 Operating conditions777.5 Cooling system requirements78ANNEX A79A MIC590 Board79A.1 Introduction79A.2 MIC590 functional capabilities79A.3 External view of MIC590 mezzanine board80A.4 Functional units of MIC59081A.5 CompactPCI connector of MIC590 board83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |     |

| 7.1.3 Board cooling recommendations.767.2 Power consumption of CPC510.777.3 Compliance with safety requirements for CPC510.777.4 Operating conditions.777.5 Cooling system requirements.78ANNEX A.79A MIC590 Board.79A.1 Introduction.79A.2 MIC590 functional capabilities.79A.3 External view of MIC590 mezzanine board.80A.4 Functional units of MIC590.81A.5 CompactPCI connector of MIC590 board.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                           |     |

| 7.2 Power consumption of CPC510.777.3 Compliance with safety requirements for CPC510.777.4 Operating conditions.777.5 Cooling system requirements.78ANNEX A.79A MIC590 Board.79A.1 Introduction.79A.2 MIC590 functional capabilities.79A.3 External view of MIC590 mezzanine board.80A.4 Functional units of MIC590.81A.5 CompactPCI connector of MIC590 board.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7.1.2 Heat dissipation by neat sink and system enclosure  | .70 |

| 7.3 Compliance with safety requirements for CPC510.777.4 Operating conditions.777.5 Cooling system requirements.78ANNEX A.79A MIC590 Board.79A.1 Introduction.79A.2 MIC590 functional capabilities.79A.3 External view of MIC590 mezzanine board.80A.4 Functional units of MIC590.81A.5 CompactPCI connector of MIC590 board.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |     |

| 7.4 Operating conditions.777.5 Cooling system requirements.78ANNEX A.79A MIC590 Board.79A.1 Introduction.79A.2 MIC590 functional capabilities.79A.3 External view of MIC590 mezzanine board.80A.4 Functional units of MIC590.81A.5 CompactPCI connector of MIC590 board.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7.2 Power consumption of CPC510                           | 77  |

| 7.5 Cooling system requirements.78ANNEX A.79A MIC590 Board.79A.1 Introduction.79A.2 MIC590 functional capabilities.79A.3 External view of MIC590 mezzanine board.80A.4 Functional units of MIC590.81A.5 CompactPCI connector of MIC590 board.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |     |

| ANNEX A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                           |     |

| A MIC590 Board79A.1 Introduction79A.2 MIC590 functional capabilities79A.3 External view of MIC590 mezzanine board80A.4 Functional units of MIC59081A.5 CompactPCI connector of MIC590 board83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |     |

| A.1 Introduction79A.2 MIC590 functional capabilities79A.3 External view of MIC590 mezzanine board80A.4 Functional units of MIC59081A.5 CompactPCI connector of MIC590 board83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |     |

| A.2 MIC590 functional capabilities.79A.3 External view of MIC590 mezzanine board.80A.4 Functional units of MIC590.81A.5 CompactPCI connector of MIC590 board.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |     |

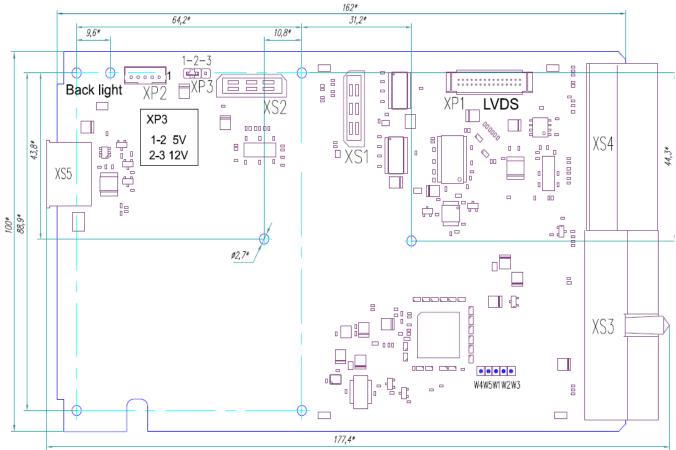

| A.3 External view of MIC590 mezzanine board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                           |     |

| A.4 Functional units of MIC590                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           |     |

| A.5 CompactPCI connector of MIC590 board83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A.5 CompactPCI connector of MIC590 board                  | .83 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |     |

| B. Useful Abbreviations, Acronyms and Short-Cuts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           | -   |

# List of tables

| Table 1-1: CPC510 hardware configurations                                                   | .,15 |

|---------------------------------------------------------------------------------------------|------|

| Table 2-1: Interface modules used for improvement of CPC510 I/O functionalities             | 28   |

| Table 2-2: Addresses of SMBus devices                                                       | 37   |

| Table 2-3: Purpose of the XS6 connector's contacts for installation of MIC584               | 40   |

| Table 2-4: Purpose of USB1 and USB2 connector contacts located on the front panel of CPC510 | 42   |

| Table 2-4-1: Purpose of DisplayPort connector contacts                                      | 43   |

| Table 2-5: Purpose of Gigabit Ethernet connector contacts                                   | 45   |

| Table 2-6: Designation and functions of LEDs of CPC510                                      | 47   |

| Table 2-7: GP LED configuration and control registers P                                     | 47   |

| Table 2-8: Designation of LED register control bits                                         | 49   |

| Table 2-9: Combinations of GP indicator's control bits                                      | 49   |

| Table 5-1: Possible options of CPC510 board configuration using SA1 switch                  | 73   |

| Table 7-1: Power consumption parameters of CPC510                                           | 78   |

| Table 7-2: Parameters of the climatic and mechanical parameters (CPC510)                    | 79   |

| Annex B                                                                                     | 85   |

# List of figures

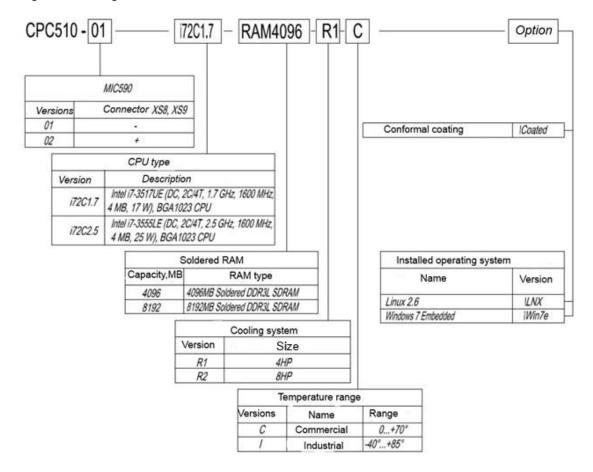

| Fig. 1-1: Configuration table of CPC510                                                             | 15 |

|-----------------------------------------------------------------------------------------------------|----|

| Fig. 1-2: External view of CPC510-01with the installed heat sink R1                                 | 18 |

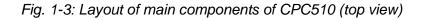

| Fig. 1-3: Layout of main components of CPC510 (top view)                                            | 19 |

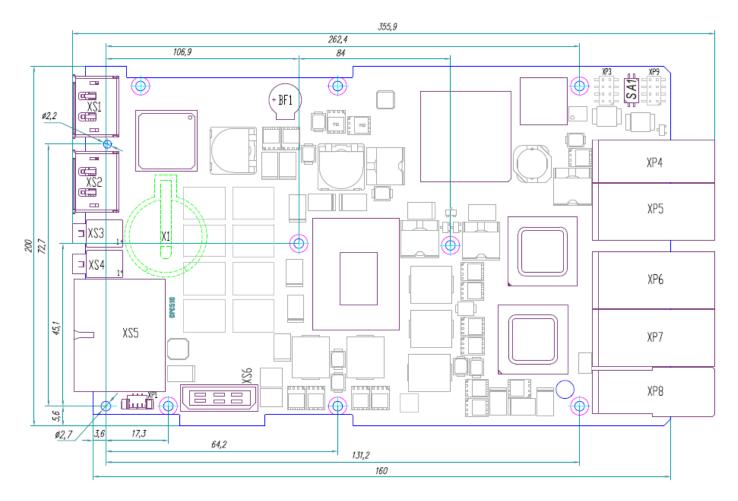

| Fig. 1-4: Layout of CPC510 main components (top view)                                               | 20 |

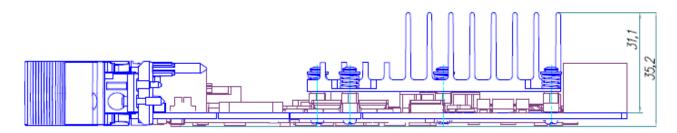

| Fig. 1-5: CPC510-01 board with the installed heat sink R1                                           |    |

| Fig. 1-6: CPC510-01 Board with the installed heat sink R2 (8HP)                                     |    |

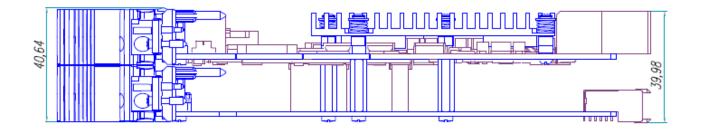

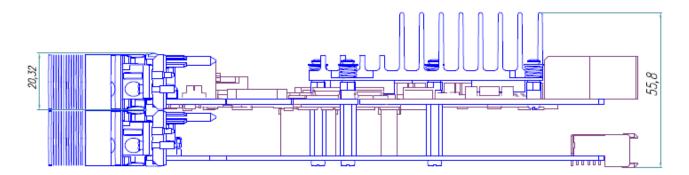

| Fig. 1-7: CPC510-02 Board with the installed heat sink R1 (4HP) and MIC590                          | 22 |

| Fig. 1-8: CPC510-02 Board with the installed heat sink R2 (8HP) and MIC590                          |    |

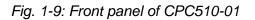

| Fig. 1-9: Front panel of CPC510-01                                                                  | 23 |

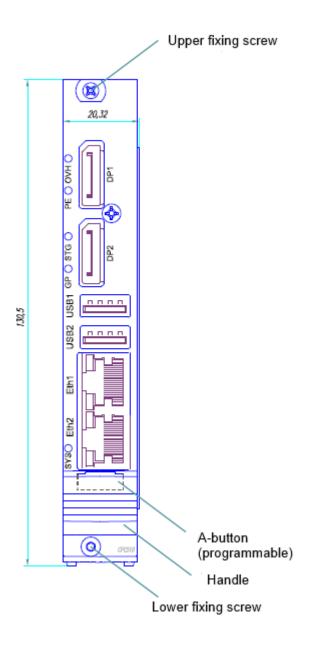

| Fig. 1-10: Front panel of CPC510-02.                                                                |    |

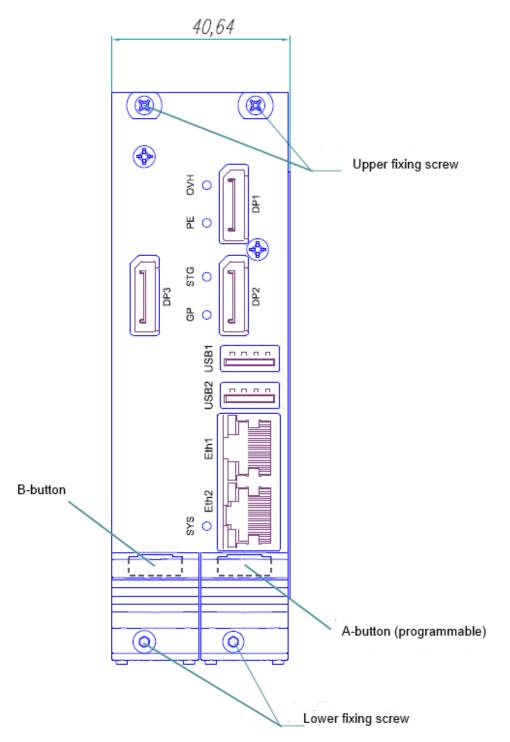

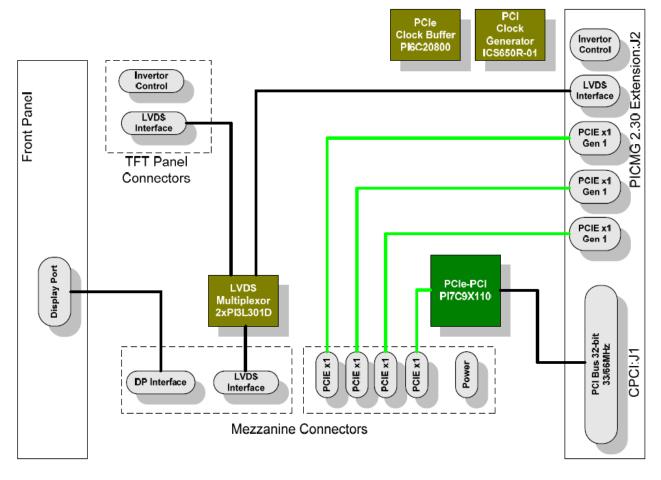

| Fig. 2-1: Block-diagram of CPC510                                                                   |    |

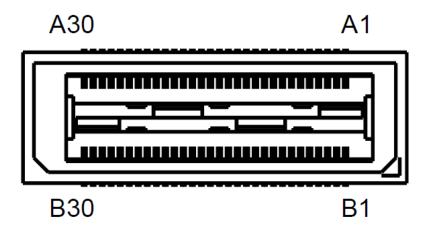

| Fig. 2-2: XS6 connector for installation of MIC584 mezzanine board                                  | 40 |

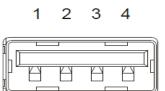

| Fig. 2-3: USB1, USB2 connectors                                                                     |    |

| Fig. 2-4: DisplayPort connector                                                                     |    |

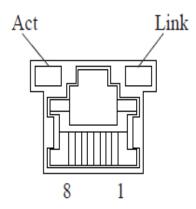

| Fig. 2-5: External view of RJ45 Ethernet connector                                                  |    |

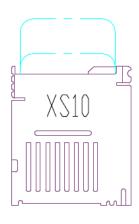

| Fig. 2-6: External view of MicroSD connector                                                        |    |

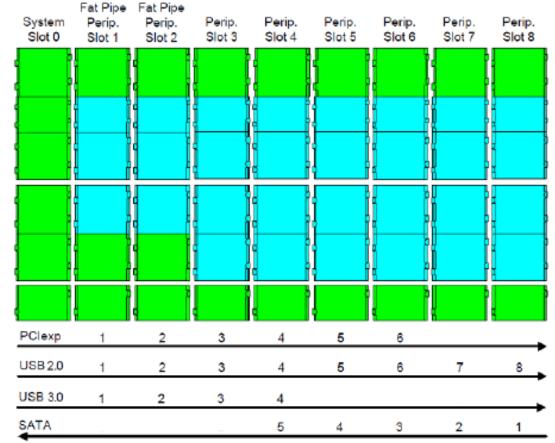

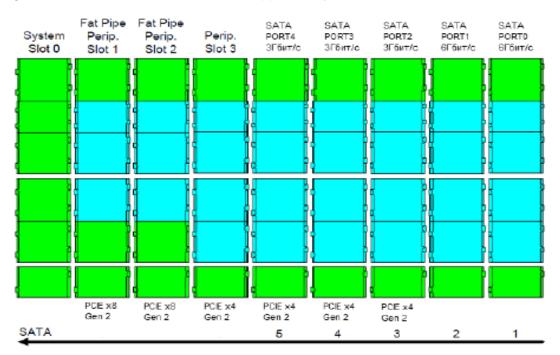

| Fig. 3-1: Numbering of CPC510 interfaces in the Compact PCI Serial backplane                        |    |

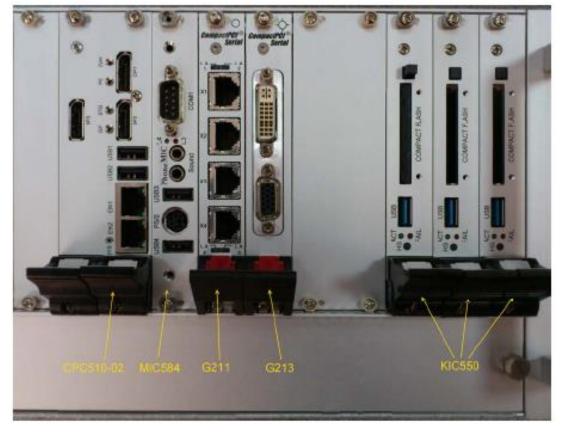

| Fig. 3-2: Example of standard implementation of Compact PCI Serial system                           |    |

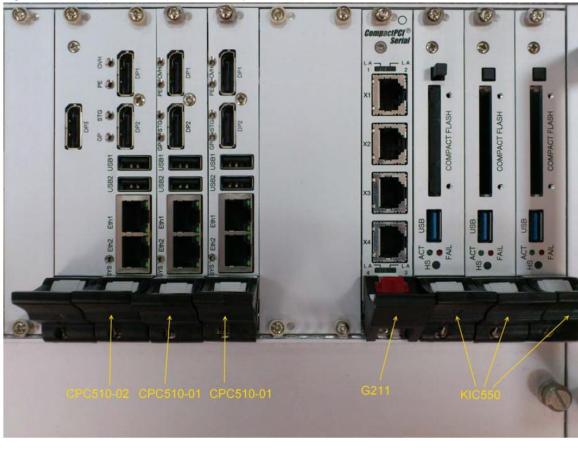

| Fig. 3-3: Example of multiprocessor system implementation                                           |    |

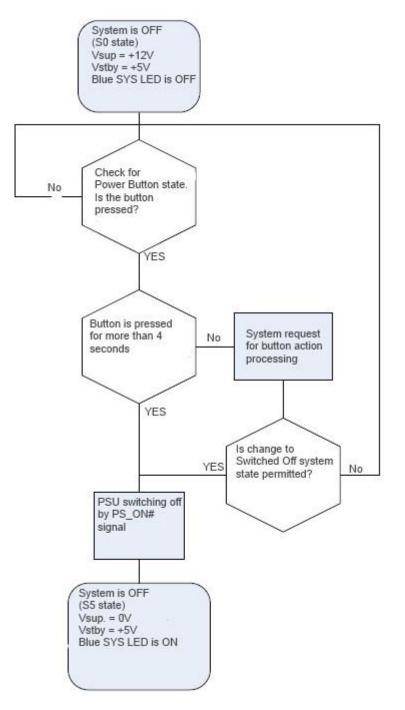

| Fig. 3-4: Algorithm of the initial system start-up from "Manual switching-off" position (D3)        |    |

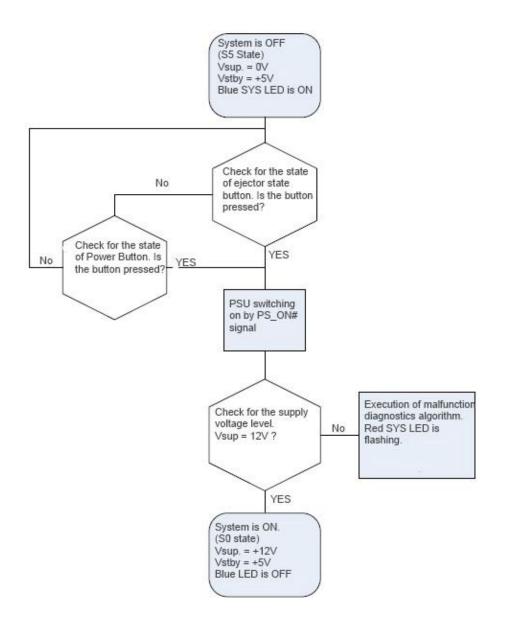

| Fig. 3-5: Algorithm of system switching-off by ejector handle or soft-based via ACPI                |    |

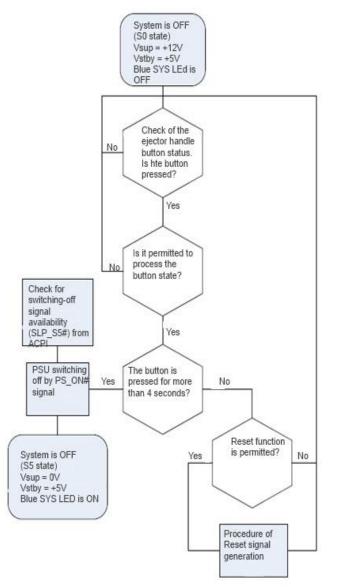

| Fig. 3-6: System switching-off algorithm by Power Button                                            |    |

| Fig. 3-7: Algorithm of system switching-on from Soft ON (S5)                                        |    |

| Fig. 3-8: Backplane SATA-interfaces supported by CPC510                                             |    |

| Fig. 3-9: Installation of CPC510-02 into two slots                                                  |    |

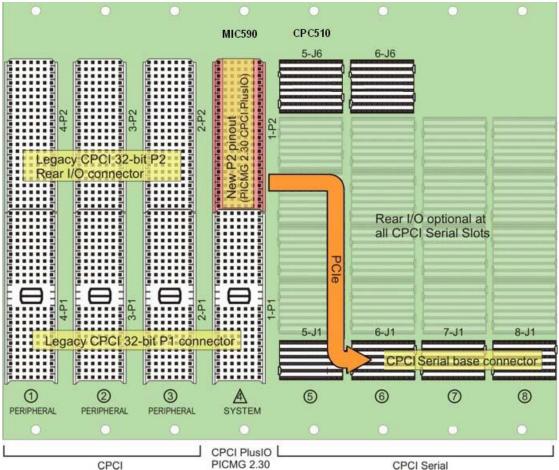

| Fig. 3-10: Example of system generation on the basis of PICMG 2.30 backplane (Plus I/O) and CPC510- |    |

| CPU board                                                                                           |    |

| Fig. 3-11: Example of PICMG 2.30 system generation with the main CPC506-03 CPU board and addition   |    |

| on-board CPC510-01 computing device                                                                 |    |

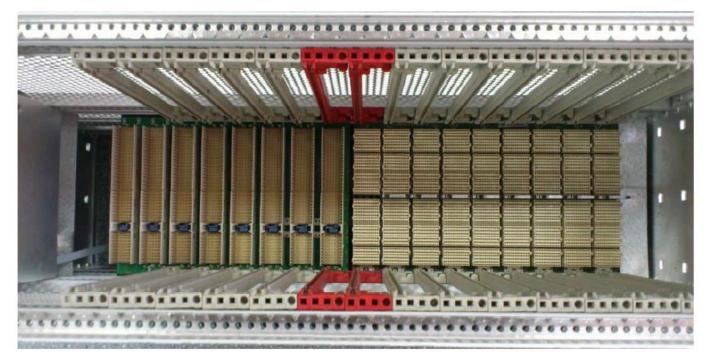

| Fig. 3-12: Example of the assembled backplanes in the extended hybrid system                        |    |

| Fig. 5-1: Switch of SA1 operating mode of CPC510                                                    |    |

| Fig. A-1: MIC590 board (side that faces CPC510).                                                    |    |

| Fig. A-2: Block diagram of MIC590                                                                   |    |

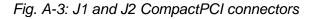

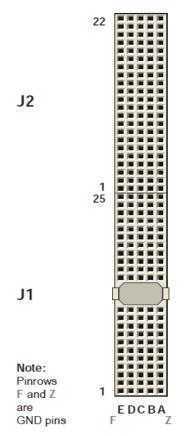

| Fig. A-3: J1 and J2 CompactPCI connectors                                                           | 83 |

|                                                                                                     |    |

All information in this document is provided for reference only, with no warranty of its suitability for any specific purpose. This information has been thoroughly checked and is believed to be entirely reliable and consistent with the product that it describes. However, Fastwel accepts no responsibility for inaccuracies, omissions or their consequences, as well as liability arising from the use or application of any product or example described in this document.

Fastwel Co. Ltd. reserves the right to change, modify, and improve this document or the products described in it, at Fastwel's discretion without further notice. Software described in this document is provided on an "as is" basis without warranty. Fastwel assumes no liability for consequential or incidental damages originated by the use of this software.

This document contains information, which is property of Fastwel Co. Ltd. It is not allowed to reproduce it or transmit by any means, to translate the document or to convert it to any electronic form in full or in parts without antecedent written approval of Fastwel Co. Ltd. or one of its officially authorized agents.

Fastwel and Fastwel logo are trademarks owned by Fastwel Co. Ltd., Moscow, Russian Federation. Ethernet is a registered trademark of Xerox Corporation. IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers Inc. Intel is a trademark of Intel Corporation. Pentium M and Celeron M are trademarks of Intel Corporation. Microsoft is a trademark of the Microsoft corporation. In addition, this document may include names, company logos and trademarks, which are registered trademarks and, therefore, are property of their respective owners.

Fastwel welcomes suggestions, remarks and proposals regarding the form and the content of this Manual.

# Trademarks

"Fastwel" logotype is a trademark belonging to Fastwel Group Co. Ltd., Moscow, Russian Federation.

Besides, this document may contain names, corporate logotypes and trademarks being registered trademarks; consequently, property rights to them belong to their respective legitimate owners.

# **Ownership Rights**

This document contains information being the property of Fastwel Group Co. Ltd. It can neither be copied nor transferred with the utilization of known media nor be stored in data storage and search systems without the prior written authorization of Fastwel Group Co. Ltd. To our best knowledge, the data in this document does not contain errors. However, Fastwel Group Co. Ltd cannot take responsibility for any inaccuracies and their consequences, as well as responsibility arising as a result of utilization or application of any diagram, product or example cited in this document. Fastwel Group Co. Ltd reserves the right to alter and update both this document and the product presented therein at its own discretion without additional notification.

# Copyright

This document cannot be copied, reproduced, transferred or converted to any electronic or machine-readable form without prior written permission of Fastwel Co. Ltd

# **NOTATIONS**

# **CAUTION HIGH VOLTAGE!**

This symbol and sign warns you about the dangers related to electric discharges (> 60 V) when touching the device and its components. Non-compliance with the safety measures mentioned or prescribed by the rules may pose a danger to your life or health or could damage the product. Please read the below subparagraph related to

how to handle high voltages.

# ATTENTION! ELECTROSTATIC SENSITIVE DEVICE!

This symbol and sign informs you that the electronic boards and their components are sensitive to static electricity. Therefore, it is required to be extra extra cautious when handling and testing it so as to ensure its integrity and working capacity of the device.

# ATTENTION! HOT SURFACE!

This symbol and sign warns you about the danger of touching a hot surface of the device.

# **ATTENTION!**

This sign encourages you to pay attention to the Manual's aspects, which incomplete understanding and ignoring may pose a danger to your health or could lead to the equipment damages.

#### NOTE!

This sign indicates that there are text fragments which require careful consideration.

# Safety requirements

This product of Fastwel LLC has been developed and tested in order to provide the compliance with the electric safety requirements. Its design provides for a longtime failsafe operation. The product life cycle can be sufficiently reduced due to its improper use during unpacking and installation process. Therefore, for the sake of your safety you'll need to comply with the below listed recommendations in order to provide the correct operation of the device.

# HIGH VOLTAGE SAFE HANDLING PROCEDURES

# ATTENTION!

All the works with this device should be performed only by the employees who have sufficient qualification to do it.

#### CAUTION, HIGH VOLTAGE!

Before installing the board into the system, please make sure that the mains supply has been switched off. This also refers to installation of mezzanine boards. In the course of installation, repairs and maintenance of the device there is a serious risk of electric shock therefore always unplug the power cord at the time of operation. This other fonder applies

also refers to other feeder cables.

# **BOARD HANDLING PROCEDURES**

### Electrostatic Sensitive Device (ESD).

The electronic boards and their components are sensitive to the static electricity. Therefore it is required to pay additional attention while handling these devices in order to ensure their safety and operability.

- Store this product in its protective packaging while it is not used for operational purposes.

- If possible, unpack or pack this product only at EOS/ESD safe workplaces. Otherwise, it is important to be electrically discharged before touching the product. This can be done by touching a metal part of your system case with your hand or tool. It is particularly important to observe antistatic precautions when setting jumpers or replacing components.

- If the product contains batteries for RTC or memory back-up, ensure that the module is not placed on conductive surfaces, including antistatic mats or sponges. This can cause short-circuit and result in damage to the battery and PCB.

# TRANSPORTATION, UNPACKING AND STORAGE

# Transportation

The device should be transported in original manufacturer's separate packaging (transport packaging), which contains an individual antistatic bag and a cardboard box, in the closed transport (automobile, railway, air transportation in heated and pressurized compartments) in storage conditions 5 defined in the IEC 721-2-1 standard (GOST standard 15150-69) or in storage conditions 3 during sea transportation.

The packaged modules should be transported in accordance with the shipping rules, specified for this particular type of transport.

During handling and transportation operations, the packaged modules should not undergo sharp pounding, falls, shocks and exposure to atmospheric precipitation. The goods should be stored in a carrier vehicle in such a manner which will prevent their moving.

# Unpacking

Prior to unpacking, before transportation at subzero temperature of ambient air the modules should be kept within 6 hours under storage conditions 1 defined in the IEC 721-2-1 standard (GOST standard 15150-69).

It is prohibited to place the packaged module close to the heat source, prior to unpacking. Retain all original packaging at least until the warranty period is over. You may need it for shipments or for storage of the product.

After unpacking the product, you should inspect it for visible damage that could have occurred during shipping or unpacking. If damage is observed (usually in the form of bent component leads or loose socketed components), contact Fastwel's official distributor from which you have purchased the product for additional instructions.

# Storage

Module storage conditions for group 1 are defined in the IEC 721-2-1 standard (GOST standard 15150-69).

# MANUFACTURER'S WARRANTY

# **Warranty Liabilities**

The Manufacturer hereby guarantees the product conformity with the requirements of the 4013-025-72782511-09 technical conditions provided that the Consumer complies with the operating, storage, transportation and installation conditions and procedures, specified by the accompanying documents.

The Manufacturer hereby guarantees that the products supplied thereby are free from defects in workmanship and materials, provided operation and maintenance norms were observed during the currently established warranty period. The Manufacturer's obligation under this warranty is to repair or replace free of charge any defective electronic component being a part of a returned product. Products that broke down through the Manufacturer's fault during the warranty period will be repaired free of charge. Otherwise the Consumer will be invoiced as per the current labor remuneration rates and expendable materials cost

# **Liability Limitation Right**

The Manufacturer shall not be liable for the damage inflicted to the Consumer's property because of the product breakdown in the process of its utilization.

# **Warranty Period**

The warranty period for the products made by Fastwel Group is 24 months since the sale date (unless otherwise provided by the supply contract).

The warranty period for the custom-made products is 36 months since the sale date (unless otherwise provided by the supply contract.

# Limitation of warranty liabilities

The above warranty liabilities shall not be applied:

To the products (including software), which were repaired or were amended by the employees, that do not represent the manufacturer. Exceptions are the cases where the customer has made repairs or made amendments to the devices in the strict compliance with instructions, preliminary agreed and approved by the manufacturer in writing;

To the products, broken down due to unacceptable polarity reversal (to the opposite sign) of the power supply, improper operation, transportation, storage, installation, mounting or accident.

# Returning a product for repair

1. Apply to Fastwel company or to any of the Fastwel's official representatives for the Product Return Authorization.

2. Attach a failure inspection report with a product to be returned in the form, accepted by the Manufacturer, with a description of the failure circumstances and symptoms.

3. Place the product in the consumer packaging (antistatic bag) and cardboard box, in which the product had been supplied. Failure to package in antistatic material will VOID all warranties of the Customer on a unilateral basis.

4. The customer pays for shipping the product to Fastwel or to an official Fastwel representative or dealer

# **1. Introduction**

# 1.1. Overview

CPC510 is a highly integrated 3U CPCI Serial solution for using in real time systems, manufacturing control, high-speed collection and processing of data. CPC510 is another product in the range of 3U CPCI modules manufactured by Fastwel Group.

The board is based on the Intel Ivy Bridge CPU (2- or 4-core CPUs) which has one of the highest performances in its class.

CPC510 uses high speed I/O interfaces (PCI-Express, Gigabit Ethernet) and modern technologies for video data processing. Modular structure of the device enables a flexible setting of the system for particular fields, which optimizes a price-quality relationship.

To expand CPC510 functionalities, MIC584 mezzanine module is used. Its detailed description is given in the User Manual.

Stable operation of CPC510 enables its use in all industrial applications. Components, on which CPC510 is based, are carefully selected in accordance with the embedded system applicability criteria which make the module perfectly fit for the long life cycle systems.

The module has the following structure of I/O channels:

- 2 GB/s Ethernet controllers (2x routed to the front panel);

- 12x USB 2.0 ports supporting HS, FS and LS data rates (2x on the front panel, 2x on the mezzanine, 8x on the backplane connector);

- 4x USB 3.0 ports (routed to the backplane connector)

- 6x SATA ports (4x ports are routed to the backplane connector, 1x - to the mezzanine board, 1 – switchable: backplane/mezzanine board)

- 1x DisplayPort, routed to MIC590 board (to the front panel of CPC510-02)

- 1x LVDS, routed to MIC590 board

- 2x DisplayPorts on the front panel.

- HD Audio, routed to the mezzanine connector.

- LPC, routed to the mezzanine connector.

# **1.2. Technical characteristics**

# - Intel Ivy Bridge CPU (with 2 or 4 cores)

# - RAM:

- DDR3 SDRAM 1333, 1600 MHz or DDR3L SDRAM 1066, 1333 MHz with ECC, up to 8 GB, soldered, 2x channels.

# - Video output (simultaneous output to 3 displays):

- 2x DisplayPort connectors (resolution up to 2560x1600@60 Hz), routed to the front panel.

- DisplayPort Interface (resolution up to 2560x1600@60 Hz), routed to MIC590 board (to the front panel of CPC510-02)

- LVDS interface dual channel 25-112 MHz, 18/24 bit/pixel (compatible with ANSI/TIA/EIA-644 specification), routed to MIC590 (LVDS connector is located on MIC590 board, CPC510-02 version, see Fig. A-1)

# - LPC bus

- Routed to the mezzanine connector

# - PCI-E bus

- Processor hosts. Support of PCI-E 2.0 (up to 5 GT/s)

- Routed via PCI-E switch to J1 and J2 CPCI Serial connectors supporting up to two devices x8

- Support of the Non-Transparent operation mode for FatPipe#1